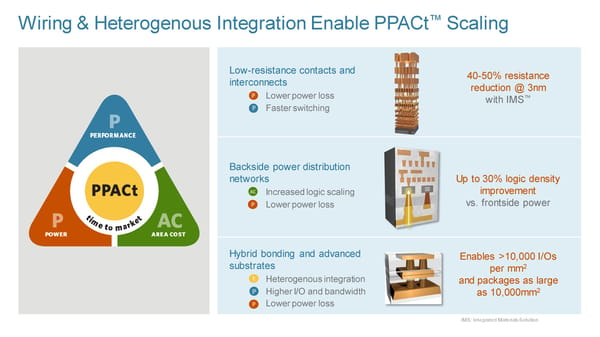

Wiring & Heterogenous Integration Enable PPACt™ Scaling Low-resistance contacts and 40-50% resistance interconnects reduction @ 3nm • Lower power loss ™ • Faster switching with IMS Backside power distribution networks Up to 30% logic density • Increased logic scaling improvement • Lower power loss vs. frontside power Hybrid bonding and advanced Enables >10,000 I/Os substrates 2 per mm • Heterogenous integration and packages as large • Higher I/O and bandwidth 2 as 10,000mm • Lower power loss IMS: Integrated Materials Solution

New Ways to Wire and Integrate Chips Page 50 Page 52

New Ways to Wire and Integrate Chips Page 50 Page 52